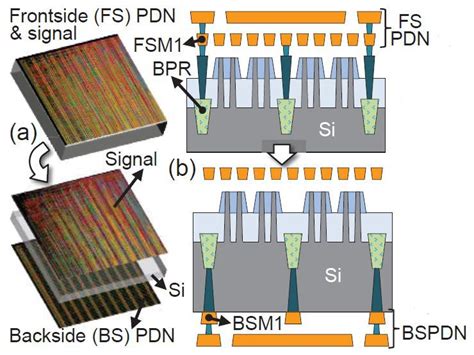

Die Welt der Halbleitertechnologie erlebt eine bedeutende Evolution mit der Einführung der 1,6-Nanometer-Prozesstechnologie durch TSMC, ein Meisterstück, das nicht nur technische Brillanz demonstriert, sondern auch ein neues Kapitel in der Energieeffizienz und Leistungssteigerung aufschlägt. Dieser Durchbruch ist besonders bemerkenswert, da er sich die innovative Technik des ‘Backside Power Delivery’ zunutze macht. Bei diesem Ansatz wird die Stromzuführung im Gegensatz zur herkömmlichen Methode, bei der Power und Signalpfade auf derselben Seite des Chips angeordnet sind, auf die Rückseite des Chips verlegt. Dies ermöglicht eine effizientere Trennung und Optimierung der elektrischen Pfade, wodurch Probleme wie Rauschen und Signalinterferenz verringert werden, die bei herkömmlichen Designs auftreten können.

Die Trennung der Energieströme von den Signalpfaden durch die Verlagerung auf die Rückseite des Chips ist eine Konzeptänderung, die tiefgreifende Auswirkungen auf die Chiparchitektur hat. Einerseits ermöglicht es größere und weniger widerstandsbehaftete Leiterbahnen, die mehr Energie liefern können, was zu einer gesteigerten Leistung führt. Andererseits kann diese Neuerung die Wärmeableitung erschweren, was eine sorgfältige thermische Managementstrategie erfordert. Diese technologische Neuerung birgt jedoch das Potenzial zur Leistungssteigerung und Energieeinsparung, was sie besonders attraktiv für hochleistungsintensive Anwendungen wie KI und Hochleistungsrechenzentren macht.

Einige technische Herausforderungen stehen jedoch im Raum, wie die präzise Ausrichtung von winzigen Drähten durch unzählige mikroskopisch kleine Löcher, die exakt auf beiden Seiten des Chips ausgerichtet sein müssen. Diese enorme Präzision auf Nanometerniveau erforderlich zu machen, zeigt die hohe Komplexität, die mit dieser innovativen Technik verbunden ist. Die Notwendigkeit, solch feine Details zu managen, könnte ohne den Fortschritt in der Präzisionsfertigung und Mikrofabrikation nicht bewältigt werden, was wiederum die fortlaufenden Investitionen in Forschung und Entwicklung unterstreicht.

In der Rückschau, warum eine solche Entwicklung nicht schon Jahrzehnte zuvor stattfand, fällt auf, dass die Anforderungen an Chips früher viel geringer waren sowohl in Bezug auf Leistung als auch auf Transistordichte. Die technologischen und materiellen Grenzen damaliger Zeiten erlaubten nicht die Realisierung einer solchen Technologie. Es geht hier nicht nur um das ‘Was’, sondern insbesondere um das ‘Wie’. Mit moderneren und leistungsfähigeren Fertigungstechniken können heute Probleme angegangen werden, die früher unüberwindbar schienen.

Darüber hinaus stellt diese Technologie einen Wendepunkt im Wettbewerb der Halbleiterindustrie dar, insbesondere zwischen den Titanen wie TSMC und Intel. Während Intel bereits angekündigt hatte, Technologien wie diese zu nutzen, könnte TSMC mit der kommerziellen Einführung seiner 1.6nm-Technologie möglicherweise einen kritischen Vorsprung erlangen. Dies illustriert nicht nur die Geschwindigkeit des technologischen Fortschritts in der Halbleiterindustrie, sondern auch, wie strategisch wichtige Innovationen als Hebel in einem intensiven Wettbewerbsumfeld eingesetzt werden können.

Die Entscheidung für Backside Power Delivery könnte langfristig als ein kluger Schachzug gesehen werden, der den Weg für die nächste Generation von Hochleistungs- und Energieeffizienten Chips ebnet. Es symbolisiert eine Ära, in der physikalische Grenzen kontinuierlich erweitert werden, um den stetig wachsenden Anforderungen der modernen Technologie gerecht zu werden. Die Halbleiterindustrie steht an der Schwelle zu einer Transformation, die nicht nur die technischen Möglichkeiten erweitert, sondern auch die Art und Weise, wie wir Energieeffizienz auf Mikroebene verstehen und anwenden.

Leave a Reply